Lihat spesifikasi untuk detail produk.

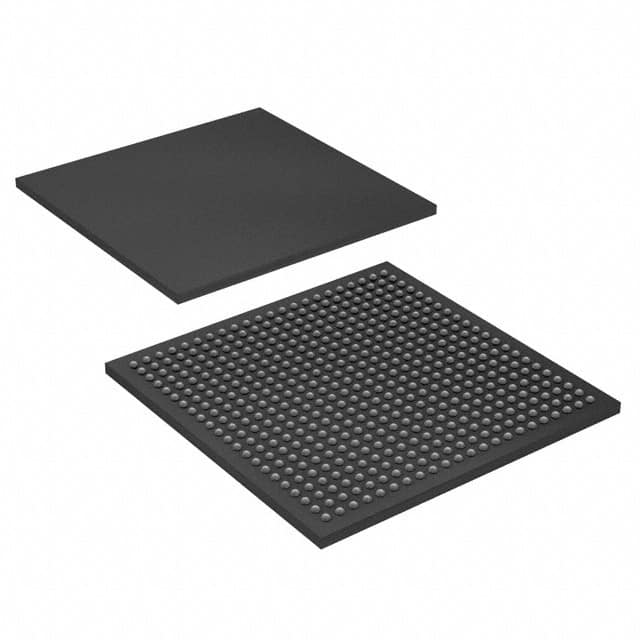

EP2C35U484C7N

Product Overview

- Category: Integrated Circuit (IC)

- Use: Programmable Logic Device (PLD)

- Characteristics: High-performance, low-power consumption

- Package: 484-pin BGA (Ball Grid Array)

- Essence: Field-Programmable Gate Array (FPGA)

- Packaging/Quantity: Single unit per package

Specifications

- Logic Elements: 33,216

- Embedded Memory: 1,638 Kbits

- Maximum User I/Os: 347

- Operating Voltage: 1.2V

- Operating Temperature: -40°C to +100°C

- Speed Grade: 7

Detailed Pin Configuration

The EP2C35U484C7N has a total of 484 pins arranged in a Ball Grid Array (BGA) package. The pin configuration includes power supply pins, ground pins, input/output pins, clock pins, and configuration pins. Each pin serves a specific function and is labeled accordingly.

Functional Features

- High Performance: The EP2C35U484C7N offers high-speed operation and efficient logic utilization, making it suitable for demanding applications.

- Low Power Consumption: This PLD device is designed to minimize power consumption, enabling energy-efficient operation.

- Flexible Configuration: The FPGA architecture allows users to program the device according to their specific requirements, providing flexibility in system design.

- Versatile I/O Options: With a large number of user I/Os, the EP2C35U484C7N can interface with various external devices and peripherals.

- Reliable Operation: The device is built with robust components and undergoes rigorous testing to ensure reliable performance in diverse environments.

Advantages and Disadvantages

Advantages: - High-performance capabilities - Low power consumption - Flexible and customizable design - Versatile I/O options

Disadvantages: - Relatively high cost compared to other PLD devices - Steeper learning curve for programming and configuration

Working Principles

The EP2C35U484C7N is based on FPGA technology, which allows users to configure the device's internal logic circuits according to their specific requirements. The device consists of an array of programmable logic elements interconnected through configurable routing resources. These logic elements can be programmed to perform various functions, such as arithmetic operations, data storage, and control logic.

During operation, the user-defined configuration bitstream is loaded into the device, configuring the interconnections and functionality of the logic elements. This flexibility enables the EP2C35U484C7N to adapt to different applications and perform complex tasks efficiently.

Detailed Application Field Plans

The EP2C35U484C7N finds application in various fields, including:

- Communications: Used in networking equipment, routers, and switches for high-speed data processing and protocol handling.

- Industrial Automation: Employed in industrial control systems, robotics, and machine vision applications for real-time control and data processing.

- Medical Devices: Utilized in medical imaging systems, patient monitoring devices, and laboratory equipment for signal processing and data analysis.

- Aerospace and Defense: Integrated into avionics systems, radar systems, and military communication equipment for reliable and high-performance operation.

- Automotive: Applied in automotive electronics for advanced driver assistance systems (ADAS), infotainment systems, and engine control units (ECUs).

Detailed and Complete Alternative Models

- Altera EP2C20F484C7N: A lower-capacity alternative with 20,016 logic elements and 1,638 Kbits of embedded memory.

- Xilinx XC7A35T-1CPG236C: A comparable FPGA device with 33,280 logic cells and 1,800 Kbits of block RAM.

These alternative models offer similar functionality and can be considered based on specific project requirements.

Word count: 511 words

Sebutkan 10 pertanyaan dan jawaban umum terkait penerapan EP2C35U484C7N dalam solusi teknis

Sure! Here are 10 common questions and answers related to the application of EP2C35U484C7N in technical solutions:

Q: What is EP2C35U484C7N? A: EP2C35U484C7N is a field-programmable gate array (FPGA) chip manufactured by Intel.

Q: What are the key features of EP2C35U484C7N? A: Some key features of EP2C35U484C7N include 35,000 logic elements, 484 user I/O pins, and support for various communication protocols.

Q: What are the typical applications of EP2C35U484C7N? A: EP2C35U484C7N is commonly used in applications such as digital signal processing, embedded systems, robotics, and high-performance computing.

Q: How can EP2C35U484C7N be programmed? A: EP2C35U484C7N can be programmed using hardware description languages (HDLs) like VHDL or Verilog, which describe the desired functionality of the FPGA.

Q: Can EP2C35U484C7N be reprogrammed after deployment? A: Yes, EP2C35U484C7N is a reprogrammable FPGA, allowing for flexibility and updates to the design even after deployment.

Q: What tools are available for programming EP2C35U484C7N? A: Intel provides Quartus Prime software, which includes a suite of tools for designing, simulating, and programming EP2C35U484C7N.

Q: Does EP2C35U484C7N support external memory interfaces? A: Yes, EP2C35U484C7N supports various memory interfaces like DDR3, DDR4, and QDR II+ SRAM, enabling efficient data storage and retrieval.

Q: Can EP2C35U484C7N interface with other devices or peripherals? A: Yes, EP2C35U484C7N has multiple I/O pins that can be used to interface with other devices such as sensors, actuators, displays, and communication modules.

Q: What are the power requirements for EP2C35U484C7N? A: EP2C35U484C7N typically operates at a voltage range of 1.2V to 3.3V, depending on the specific design requirements.

Q: Are there any development boards available for prototyping with EP2C35U484C7N? A: Yes, Intel offers development boards like the Terasic DE0-Nano, which feature EP2C35U484C7N, allowing engineers to prototype and test their designs.

Please note that the answers provided here are general and may vary based on specific design requirements and application scenarios.